Why It Matters

In advanced semiconductor design, a minor oversight at the front-end can become a major roadblock during later stages such as synthesis, place & route, or timing closure. Our verification methodologies focus on:

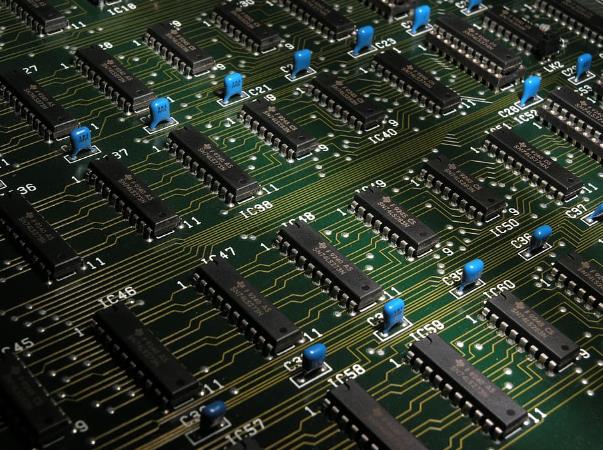

At VLSI Monks, we understand that the foundation of any successful semiconductor design lies in robust and exhaustive front-end verification. Our Frontend Verification services are engineered to ensure that your digital designs function exactly as intended — right from the earliest stages of the development cycle.

Frontend verification is the process of validating the Register Transfer Level (RTL) representation of your design to detect and eliminate bugs, logical mismatches, and functional inconsistencies before they propagate further into the design flow. It’s a critical step in the VLSI ASIC/SoC lifecycle that prevents costly errors later in implementation and silicon verification.

In advanced semiconductor design, a minor oversight at the front-end can become a major roadblock during later stages such as synthesis, place & route, or timing closure. Our verification methodologies focus on:

At VLSI Monks, our verification team brings deep domain expertise to every project. We offer a wide spectrum of front-end verification services including:

We verify your RTL using structured verification environments to confirm that the logic behaves as per design intent.

Our engineers develop advanced testbenches using SystemVerilog and the Universal Verification Methodology (UVM) to perform comprehensive stimulus, checking, and coverage analysis.

We combine formal techniques with simulation-based functional verification to boost confidence in your design’s correctness across all operating scenarios.

To handle complex interfaces, our team develops reusable Verification IPs, ensuring accurate and standardized protocol validation.

For final validation, we offer gate-level simulation services to ensure that the post-synthesis netlist aligns with functional expectations.

Lorem ipsum dolor sit amet, conse ctetur adipiscing elit. Ut elit tellus off, luctus nec ullamc orper mattis, pvinar dapibus leo.

Lorem ipsum dolor sit amet, conse ctetur adipiscing elit. Ut elit tellus off, luctus nec ullamc orper mattis, pvinar dapibus leo.

Lorem ipsum dolor sit amet, conse ctetur adipiscing elit. Ut elit tellus off, luctus nec ullamc orper mattis, pvinar dapibus leo.

Lorem ipsum dolor sit amet, conse ctetur adipiscing elit. Ut elit tellus off, luctus nec ullamc orper mattis, pvinar dapibus leo.

Lorem ipsum dolor sit amet, conse ctetur adipiscing elit. Ut elit tellus off, luctus nec ullamc orper mattis, pvinar dapibus leo.

Lorem ipsum dolor sit amet, conse ctetur adipiscing elit. Ut elit tellus off, luctus nec ullamc orper mattis, pvinar dapibus leo.

Lorem ipsum dolor sit amet, conse ctetur adipiscing elit. Ut elit tellus off, luctus nec ullamc orper mattis, pvinar dapibus leo.

Lorem ipsum dolor sit amet, conse ctetur adipiscing elit. Ut elit tellus off, luctus nec ullamc orper mattis, pvinar dapibus leo.